運放設計十坑 信號放大器實戰避雷指南

在電子設計領域,運算放大器是信號處理與放大的核心元件。即便是經驗豐富的工程師,在運放電路設計中也難免遇到各種“坑”。本文以立創商城等常用元器件平臺為參考,結合信號放大器的典型應用場景,梳理了運放設計的十個常見陷阱,并提供了實用的解決方案。

第一坑:電源去耦不當

運放對電源噪聲極為敏感。許多設計中僅在電源引腳附近放置一個0.1μF電容,卻忽略了低頻去耦。建議采用大小電容并聯(如10μF電解電容與0.1μF陶瓷電容組合),并盡量靠近電源引腳布局,以濾除寬頻噪聲。

第二坑:忽視輸入偏置電流路徑

雙極型運放的輸入偏置電流需要明確的直流回流路徑。若采用電容耦合輸入而無直流通路,會導致輸出飽和或漂移。務必通過電阻為偏置電流提供到地的通路,尤其是在同相放大或電壓跟隨器配置中。

第三坑:未考慮共模電壓范圍

輸入信號電壓超出運放允許的共模輸入范圍時,會導致失真甚至損壞。選擇運放前,需仔細核對數據手冊中的共模電壓范圍,并確保在電源電壓和輸入信號幅度下留有足夠余量。

第四坑:輸出負載過重

運放的輸出電流能力有限。直接驅動低阻抗負載(如揚聲器、電機)可能造成輸出電壓跌落、失真或過熱。需通過緩沖級(如晶體管擴流)或選擇高輸出電流運放來匹配負載需求。

第五坑:反饋網絡電阻取值不當

反饋電阻過大(如>1MΩ)會加劇噪聲、漂移和寄生電容影響;過小(如<1kΩ)則會增加功耗并加重運放輸出負擔。通常建議在1kΩ至100kΩ之間選擇,并保持同相端與反相端直流電阻平衡以減少偏置電流引起的誤差。

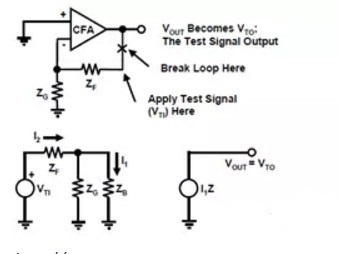

第六坑:忽略帶寬與壓擺率限制

對于高頻信號,需同時關注增益帶寬積(GBW)和壓擺率(Slew Rate)。即使小信號帶寬足夠,大信號下壓擺率不足仍會導致波形失真。應根據信號頻率與幅度,選擇GBW和壓擺率均有余量的運放型號。

第七坑:PCB布局引入噪聲

糟糕的布局會引入寄生電容、電感耦合和地線噪聲。關鍵措施包括:縮短高頻信號走線、模擬地與數字地單點連接、避免敏感走線與電源或數字線路平行、為高阻抗節點設置保護環(Guard Ring)。

第八坑:單電源應用未設置虛地

單電源供電時,若輸入信號為交流,需通過電阻分壓或專用基準芯片建立中間電平的“虛地”(通常為Vcc/2),并用電容去耦,以確保信號在運放的線性范圍內擺動。

第九坑:溫度漂移未補償

在精密放大電路中,運放的輸入失調電壓和偏置電流會隨溫度變化,導致輸出漂移。可通過選擇低溫漂運放(如自動調零、斬波穩零型)、采用匹配電阻網絡或軟件校準來抑制溫漂影響。

第十坑:ESD防護缺失

運放輸入引腳通常很脆弱,易受靜電放電(ESD)損傷。在可能接觸靜電的環境(如測試接口、外接傳感器),應添加TVS管、限流電阻或ESD保護二極管,確保電路可靠性。

成功的運放設計始于對器件特性的深入理解,成于嚴謹的電路計算與PCB布局。建議工程師在設計初期便系統考慮上述問題,充分利用立創商城等平臺提供的參數篩選與仿真模型,結合實際測試進行驗證,從而有效規避陷阱,打造穩定、高性能的信號放大器。

如若轉載,請注明出處:http://www.peixinhotelbeijing.cn/product/23.html

更新時間:2026-05-08 19:23:20